图1:本次10kV SiC MOSFET技术报告发布现场

ISPSD会议是IEEE旗下的功率半导体旗舰会议,为功率器件领域的顶级国际学术会议,议题涵盖了功率半导体器件、功率集成电路、功率集成、工艺、封装和应用等多个领域,被誉为功率半导体器件和集成电路领域的“奥林匹克会议”。本届ISPSD会议在日本九州岛熊本县举办,汇聚展示了全球功率半导体器件领域的最新研究成果。本届会议共收到投稿350篇,录用176篇,其中遴选58篇成果以大会全体报告方式发布,占比仅为16.6%。本篇论文的发表,彰显了瞻芯电子在SiC功率器件领域的创新引领地位。相关工作成果同时被半导体器件领域顶级学术期刊——IEEE Transactions on Electron Devices接收,即将发表。

关于10kV SiC MOSFET芯片

10kV等级SiC MOSFET器件在下一代智能电网、高压大容量功率变换系统等领域有广阔的应用场景。但受困于材料及工艺成熟度问题,早期的相关工作多局限于芯片功能展示,芯片面积普遍较小,通流能力较差。如何进一步增加芯片面积,并保持良好的芯片制造良率和可制造性,一直是学术界和产业界面临的巨大挑战。

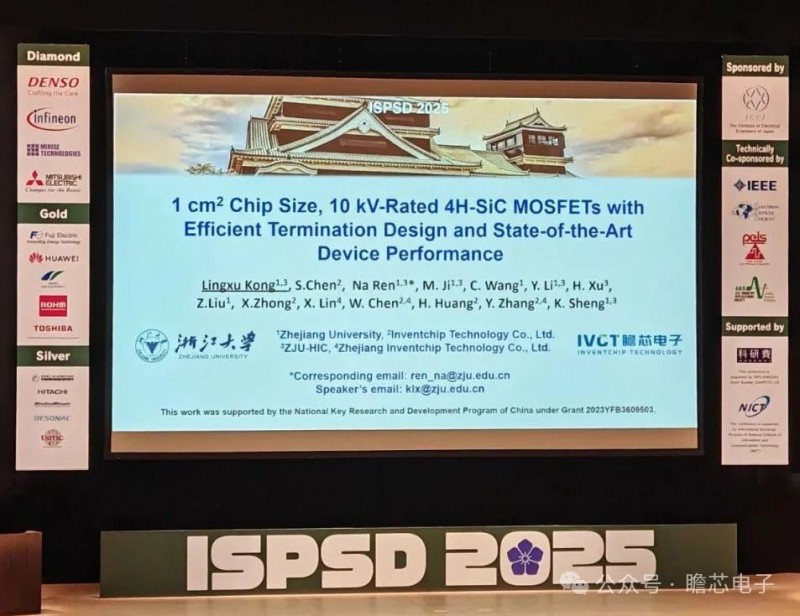

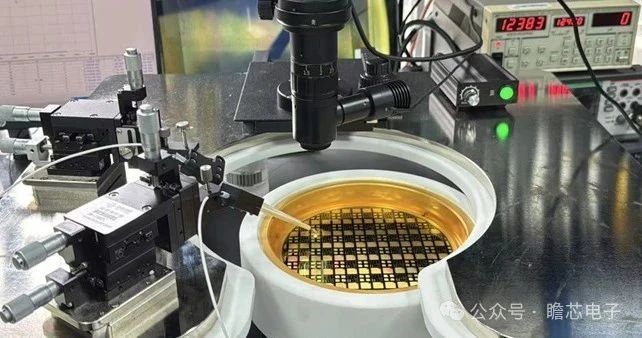

本次发表的10kV等级SiC MOSFET芯片,基于浙江瞻芯SiC晶圆厂的第三代平面栅工艺平台生产,单芯片尺寸达到10mm x 10mm,单芯片导通电流接近40A,击穿电压超过12kV,为目前公开发表的最大尺寸10kV等级SiC MOSFET芯片。芯片核心性能指标,比导通电阻(Ron.sp)小于120mΩ·cm2 ,接近SiC材料的理论极限。在芯片制造层面,芯片采用高能离子注入工艺,配合窄JFET区域设计,有效解决了高压SiC器件在击穿电压和导通电阻之间的矛盾。在芯片设计层面,芯片优化了高压终端结构,极大地提升了芯片终端效率并降低了制造难度。

图3:本次成果与历史成果对比(黄色虚线为SiC材料理论极限)

本项工作通过上述一系列工艺和设计创新,实现了更大芯片尺寸、更大通流能力、更高良率水平的10kV SiC MOSFET技术,将提升下一代智能电网、高压大容量功率变换系统的应用潜力,为高压固态变压器、高压直流断路器等场景的应用革新提供了坚实支撑。该技术不仅有望推动相关产业链的升级,同时有助于提升能源利用效率,促进绿色能源的普及应用,为社会的可持续发展贡献力量。

本项目得到了国家重点研发计划项目(2023YFB3609503)支持。